1. Tujuan [KEMBALI]

- Mengetahui apa itu Transistor Transistor Logic.

- Mengetahui cara membuat rangkaian Transistor Transistor Logic.

2. Alat dan Bahan [KEMBALI]

- Resistor

Resistor

atau hambatan adalah salah satu komponen elektronika yang memiliki nilai

hambatan tertentu, dimana hambatan ini akan menghambat arus listrik yang mengalir melaluinya.

- Dioda

komponen aktif dua kutub yang pada umumnya bersifat semikonduktor, yang

memperbolehkan arus listrik mengalir ke satu arah (kondisi panjar maju) dan

menghambat arus dari arah sebaliknya (kondisi panjar mundur). Diode dapat

disamakan sebagai fungsi katup di dalam bidang elektronika.

- Transistor NPN

Alat semikonduktor yang dipakai

sebagai penguat, sebagai sirkuit pemutus dan penyambung arus (switching),

stabilisasi tegangan, dan modulasi sinyal.

- Logicstate

Input logika '1' dan '0' pada rangkaian proteus

- Logicprobe

Menampilkan output logika '1' dan '0' pada rangkaian proteus

3. Teori [KEMBALI]

Transistor Transistor Logic (TTL) adalah keluarga logika yang diimplementasikan dengan teknologi proses bipolar yang menggabungkan atau mengintegrasikan transistor NPN, dioda persimpangan PN dan difusi resistor dalam struktur monolitik tunggal untuk mendapatkan fungsi logika yang diinginkan. Gerbang NAND adalah blok bangunan dasar keluarga logika ini.

Subfamili yang berbeda dalam keluarga logika ini, seperti yang diuraikan sebelumnya,termasuk TTL standar, TTL daya rendah, TTL daya tinggi, Schottky TTL daya rendah, Schottky TTL, lanjutan Schottky TTL daya rendah, TTL Schottky canggih dan TTL cepat. Dalam paragraf berikut, kami akan menjelaskan secara singkat masing-masing subfamili ini dalam hal struktur dan karakteristik internal parameter.

2. Operasi Sirkuit

1. TTL Standar

Gambar diatas menunjukkan skema internal gerbang TTL NAND standar. Itu adalah salah satu dari empat sirkuit 5400/7400, yang merupakan gerbang NAND quad dua input. Rangkaian beroperasi sebagai berikut. Transistor Q1 adalah transistor NPN dua emitor, yang setara dengan dua transistor NPN dengan basis dan emitornya terminal diikat bersama. Dua emitor adalah dua input dari gerbang NAND. Dioda D2 dan D3 adalah digunakan untuk membatasi tegangan input negatif. Kami sekarang akan memeriksa perilaku rangkaian untuk berbagai status logika yang mungkin pada dua input.

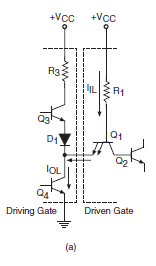

Ketika kedua input berada dalam keadaan logika TINGGI seperti yang ditentukan oleh keluarga TTL (VIH = 2 V minimum), arus mengalir melalui basis-collector PN junction diode dari transistor Q1 ke dalam basis transistor Q2. Transistor Q2 dihidupkan ke saturasi, dengan hasil bahwa transistor Q3 dimatikan dan transistor Q4 AKTIF. Ini menghasilkan RENDAH logika pada output, dengan VOL maksimum 0,4 V ketika sedang tenggelam arus 16 mA dari beban eksternal diwakili oleh input dari fungsi logika didorong oleh output. Tindakan tenggelam saat ini ditunjukkan pada Gambar 5.7 (a). Transistor Q4 juga disebut sebagai transistor saat ini tenggelam atau pull-down, untuk alasan yang jelas. Diode D1 digunakan untuk mencegah transistor Q3 dari melakukan bahkan sejumlah kecil arus ketika output RENDAH.

3. NOT Gate (or Inverter)

Gambar 5.8 menunjukkan skema internal gerbang NOT (inverter) dalam keluarga TTL standar. Itu Skema yang ditunjukkan adalah salah satu dari enam inverter dalam hex inverter (tipe 7404/5404). Internal skematis sama dengan gerbang NAND kecuali bahwa transistor input adalah tunggal normal Transistor NPN alih-alih multi-emitor.

4. AND Gate

Gambar 5.10 menunjukkan skema internal gerbang AND dalam keluarga TTL standar. Skematis yang ditunjukkan adalah salah satu dari empat gerbang AND dalam quad AND-input dua gerbang (tipe 7408/5408). Dalam urutan untuk menjelaskan bagaimana pengaturan skema ini bertindak sebagai gerbang AND, kita akan mulai dengan menyelidiki kondisi input yang akan menghasilkan output TINGGI. Output TINGGI menyiratkan Q6 berada dalam cut-off dan Q5 berada dalam konduksi. Ini bisa terjadi hanya ketika Q4 dalam cut-off. Transistor Q4 dapat dalam kondisi terputus hanya ketika Q2 dan Q3 berada dalam konduksi. Ini hanya mungkin ketika kedua input berada di logika kondisi TINGGI. Mari kita lihat apa yang terjadi ketika salah satu dari dua input didorong ke RENDAH negara. Ini mendorong Q2 dan Q3 ke kondisi cut-off, yang memaksa Q4 dan selanjutnya Q6 menjadi saturasi dan Q5 untuk memotong.

Gambar 5.9 menunjukkan skema internal gerbang NOR dalam keluarga TTL standar. Skematis yang ditunjukkan adalah salah satu dari empat gerbang NOR di quad dua input gerbang NOR (tipe 7402/5402). Di sisi input ada dua transistor terpisah, bukan transistor multi-emitor dari gerbang NAND. Masukan dimasukkan ke penghasil dua transistor, pengumpul yang lagi memberi makan basis transistor dengan kolektor dan terminal emitor mereka diikat bersama. Nilai resistansi yang digunakan sama dengan yang digunakan dalam kasus gerbang NAND.

Tahap output juga merupakan tiang totem yang sama tahap output. Sirkuit ini cukup jelas. Satu-satunya kondisi input dimana transistor Q3 dan Q4 tetap dalam cut-off, sehingga mendorong Q6 ke cut-off dan Q5 ke konduksi, adalah ketika kedua input berada dalam keadaan logika RENDAH. Output dalam kasus seperti ini adalah logika TINGGI. Untuk semua kondisi input lainnya, baik Q3 atau Q4 akan melakukan, mendorong Q6 ke saturasi dan Q5 untuk memotong, menghasilkan logika RENDAH di hasil.

6. OR Gate

Gambar 5.11 menunjukkan skema internal gerbang OR dalam keluarga TTL standar. Skema yang ditampilkan adalah salah satu dari empat gerbang OR di quad OR-input gerbang dua (tipe 7432/5432). Kami akan mulai dengan menyelidiki kondisi input yang akan menghasilkan output RENDAH. Output RENDAH menuntut Q8 jenuh dan Q7 cut-off. Ini pada gilirannya mengharuskan Q6 berada dalam saturasi dan Q5, Q4 dan Q3 berada dalam cut-off. Ini hanya mungkin ketika Q1 dan Q2 berada dalam saturasi. Artinya, kedua input berada dalam keadaan logika RENDAH.

7. Ex-OR Gerbang

Gambar 5.12 menunjukkan skema internal gerbang EX-OR dalam keluarga TTL standar. Skematis

yang diperlihatkan adalah salah satu dari empat gerbang EX-OR di gerbang EX-OR dua-input quad (tipe 7486/5486). Kami akan mencatat persamaan antara sirkuit ini dan sirkuit OR. Satu-satunya elemen baru adalah pasangan transistor yang saling berhubungan Q7 dan Q8. Kita akan melihat itu, ketika kedua inputnya baik TINGGI atau RENDAH, Q7 dan Q8 tetap terpotong. Dalam kasus input berada di logika TINGGI negara, basis dan terminal emitor dari kedua transistor ini tetap dekat potensi tanah.

8. AND-OR-INVERT Gate

Gambar 5.13 menunjukkan skema internal dua-lebar, dua-input AND-OR-INVERT atau AND-NOR gerbang. Skema yang ditampilkan adalah salah satu dari dua gerbang dalam dua-lebar, dua-input DAN-ORINVERT ganda gerbang (tipe 7450/5450). Dua transistor input multi-emitor Q1 dan Q2 menyediakan ANDing input masing-masing. Pemisah drive yang terdiri dari Q3, Q4, R3 dan R4 menyediakan fungsi OR. Itu tahap output menyediakan inversi. Jumlah penghasil emisi di masing-masing transistor input menentukan jumlah literal di masing-masing minterm dalam output jumlah-produk ekspresi Boolean. Bagaimana lebar gerbang akan ditentukan oleh jumlah transistor input, yang juga sama dengan jumlahnya dari transistor drive splitter

9. Open Collector Gate

Gerbang kolektor terbuka di TTL adalah yang tanpa tahap output totem-pole. Tahap output dalam kasing ini tidak memiliki transistor pull-up aktif. Resistor pull-up eksternal perlu dihubungkan dari terminal kolektor terbuka dari transistor pull-down ke terminal VCC. Penarik pull-up biasanya 10 k. Gambar 5.14 menunjukkan skema internal gerbang NAND dengan kolektor terbuka keluaran. Skema yang ditampilkan adalah salah satu dari empat gerbang dari NAND quad dua-input (tipe 74/5401).

10. Gerbang Tristate

Gerbang tristate memiliki tiga status keluaran, yaitu logika Status RENDAH, status logika TINGGI dan status impedansi tinggi. Input memungkinkan eksternal memutuskan apakah gerbang logika bekerja sesuai dengan tabel kebenarannya atau dalam keadaan impedansi tinggi. Gambar 5.16 menunjukkan skema internal tipikal dari inverter tristate dengan input aktif HIGH yang aktif. Sirkuit berfungsi sebagai berikut. Ketika input yang diaktifkan TINGGI, itu bias balik dioda D1 dan juga berlaku a logika TINGGI pada salah satu penghasil transistor input Q1. Rangkaian berperilaku seperti inverter. Ketika input aktifkan RENDAH, dioda D1 menjadi bias maju. A RENDAH mengaktifkan pasukan input Q2 dan Q4 untuk cut-off. Juga, D1 yang bias maju memaksa Q3 untuk memotong. Dengan kedua transistor keluaran dalam cut-off, keluaran dasarnya adalah rangkaian terbuka dan dengan demikian menghadirkan impedansi keluaran tinggi.

11. TTL Berdaya Rendah

TTL daya rendah adalah varian daya rendah dari TTL standar di mana disipasi daya lebih rendah dicapai dengan mengorbankan kecepatan operasi yang berkurang. Gambar 5.17 menunjukkan skema internal gerbang NAND TTL daya rendah. Sirkuit yang ditunjukkan adalah salah satu dari empat gerbang di dalam input dua quad NAND (tipe 74L00 atau 54L00). Sirkuit, seperti yang dapat kita lihat, sama dengan sirkuit TTL standar Gerbang NAND kecuali untuk nilai resistansi yang meningkat dari berbagai resistor yang digunakan dalam rangkaian. Nilai resistansi yang meningkat menyebabkan disipasi daya yang lebih rendah.

12. TTL Daya Tinggi (74H / 54H)

TTL daya tinggi adalah varian TTL standar daya tinggi berkecepatan tinggi di mana kecepatan ditingkatkan (Mengurangi delay propagasi) dicapai dengan mengorbankan disipasi daya yang lebih tinggi. Gambar 5.18 menunjukkan skema internal gerbang NAND TTL daya tinggi. Rangkaian yang ditunjukkan adalah salah satu dari empat gerbang di dalam NAND quad dua input (tipe 74H00 atau 54H00). Sirkuit, seperti yang bisa kita lihat, hampir sama dengan gerbang NL TTL standar kecuali untuk kombinasi transistor Q3-dioda D1 dalam tahap output totem-tiang telah digantikan oleh pengaturan Darlington yang terdiri dari Q3, Q5 dan R5. Pengaturan Darlington melakukan pekerjaan yang sama dengan dioda D1 pada tiang totem konvensional pengaturan. Ini memastikan bahwa Q5 tidak melakukan sama sekali ketika output RENDAH. Menurun nilai resistansi dari berbagai resistor yang digunakan dalam rangkaian menyebabkan disipasi daya yang lebih tinggi.

rangkaian Inverter in the standard TTL

logicstate inverter berlogika 1 maka arus dari VCC akan mengalir ke masing – masing resistor, dan arus yang masuk ke R7,R8,R9 akan mengalir ke masing – masing kaki basis transistor Q9,Q8,Q10 dan dikarenakan adanya arus basis maka ada arus yang juga mengalir pada kaki collector . arus yang mengalir pada Q9 akan mengalir ke emitter lalu ke D5 ke ground sedangkan arus pada Q8 akan mengalir ke emitter lalu ke kaki basis Q11 dan arus dari Q10 akan mengalir ke D4 lalu ke kaki collector q11 lau ke ground. Sedangkan arus kaki emitter q8 akan mengalir ke kaki basis q11 dan ke R10. pada simulasi rangkaian ini, kita harus menginputkan logika agar mendapatkan output yang diinginkan

rangkaian NOR gate in the standard TTL

jika logicstate keduanya berlogika 1 maka arus dari VCC akan mengalir ke masing – masing resistor, dan arus yang masuk ke R5,R6,R11,R13 akan mengalir ke masing – masing kaki basis transistor Q6,Q5,Q7,Q13 dan dikarenakan adanya arus basis maka ada arus yang juga mengalir pada kaki collector . arus dari r11 akan mengalir pada Q7 dan akan mengalir ke emitter lalu ke D6 lalu ke Q12 karena adanya arus basis dari Q12 maka arus dari D6 akan ke ground .sedangkan arus dari R6 akan mengalir ke Q5 dan ke Q14 dan arus pada Q5 akan mengalir ke emitter lalu ke kaki basis Q12 dan arus akan ke Resistor (r12) lalu ke ground. Sedangkan arus pada R13 akan mengalir k Q13 , karena ada arus basis pada q13 maka arus collektor yang ada pada Q14 akan mengalir lalu ke R12 dan ke ground.tetapi arus pada emitter Q6 dari D6 lalu ke ground. Sedangkan arus kaki emitter Q6 akan mengalir ke D7 lalu ke ground. pada simulasi rangkaian ini, kita menginputkan logika agar mendapatkan output yang diinginkan. Hasilnya kan didapatkan 1 ketika inputan keduanya berlogika 0 itu dikarenakan mengunakan kaidah gerbang NOR.

rangkaian OR gate in the standard TTL

jika logicstate keduanya berlogika 1 maka arus dari VCC akan mengalir ke masing – masing resistor, dan arus akan mengalir ke masing – masing kaki basis transistor dan dikarenakan adanya arus basis maka ada arus yang juga mengalir pada kaki collector . pada simulasi rangkaian ini, kita menginputkan logika agar mendapatkan output yang diinginkan. Hasilnya kan didapatkan 1 ketika inputan keduanya selain dari 0 dan 0.

5. Simulasi Rangkaian [KEMBALI]

rangkaian Inverter in the standard TTL

rangkaian AND in the standard TTL

rangkaian NOR gate in the standard TTL

rangkaian OR gate in the standard TTL

rangkaian AND in the standard TTL

rangkaian NOR gate in the standard TTL

rangkaian OR gate in the standard TTL

6. Video [KEMBALI]

rangkaian TTL Standar

rangkaian Inverter in the standard TTL

rangkaian NOR gate in the standard TTL

rangkaian AND in the standard TTL

rangkaian OR gate in the standard TTL

rangkaian NOR gate in the standard TTL

rangkaian OR gate in the standard TTL

rangkaian Ex-OR Gerbang

rangkaian AND-OR-INVERT Gate

rangkaian Open Collector Gate

rangkaian Gerbang Tristate

rangkaian TTL Berdaya Rendah

rangkaian TTL Daya Tinggi (74H / 54H)

rangkaian AND-OR-INVERT Gate

rangkaian Open Collector Gate

rangkaian Gerbang Tristate

rangkaian TTL Berdaya Rendah

rangkaian TTL Daya Tinggi (74H / 54H)

File simulasi rangkaian proteus

- Rangkaian 1

- Rangkaian 2

- Rangkaian 3

- Rangkaian 4

- Rangkaian 5

- Rangkaian 6

- Rangkaian 7

- Rangkaian 8

- Rangkaian 9

- Rangkaian 10

- Rangkaian 11

Video simulasi

- Rangkaian 1

- Rangkaian 2

- Rangkaian 3

- Rangkaian 4

- Rangkaian 5

- Rangkaian 6

- Rangkaian 7

- Rangkaian 8

- Rangkaian 9

- Rangkaian 10

- Rangkaian 11

Teori download

Datasheet 7408 download

Tidak ada komentar:

Posting Komentar